- 您现在的位置:买卖IC网 > Sheet目录1995 > DSD1792DB (Texas Instruments)IC 24BIT STEREO AUD DAC 28-SSOP

DSD1792

SLES067B MARCH 2003 REVISED NOVEMBER 2006

www.ti.com

33

IOUT–

Figure 34

Circuit

IOUT+

IOUTL– (Pin 26)

IOUTL+ (Pin 25)

OUT+

1

2

3

Balanced Out

IOUT–

Figure 34

Circuit

IOUT+

IOUTR– (Pin 18)

IOUTR+ (Pin 17)

OUT–

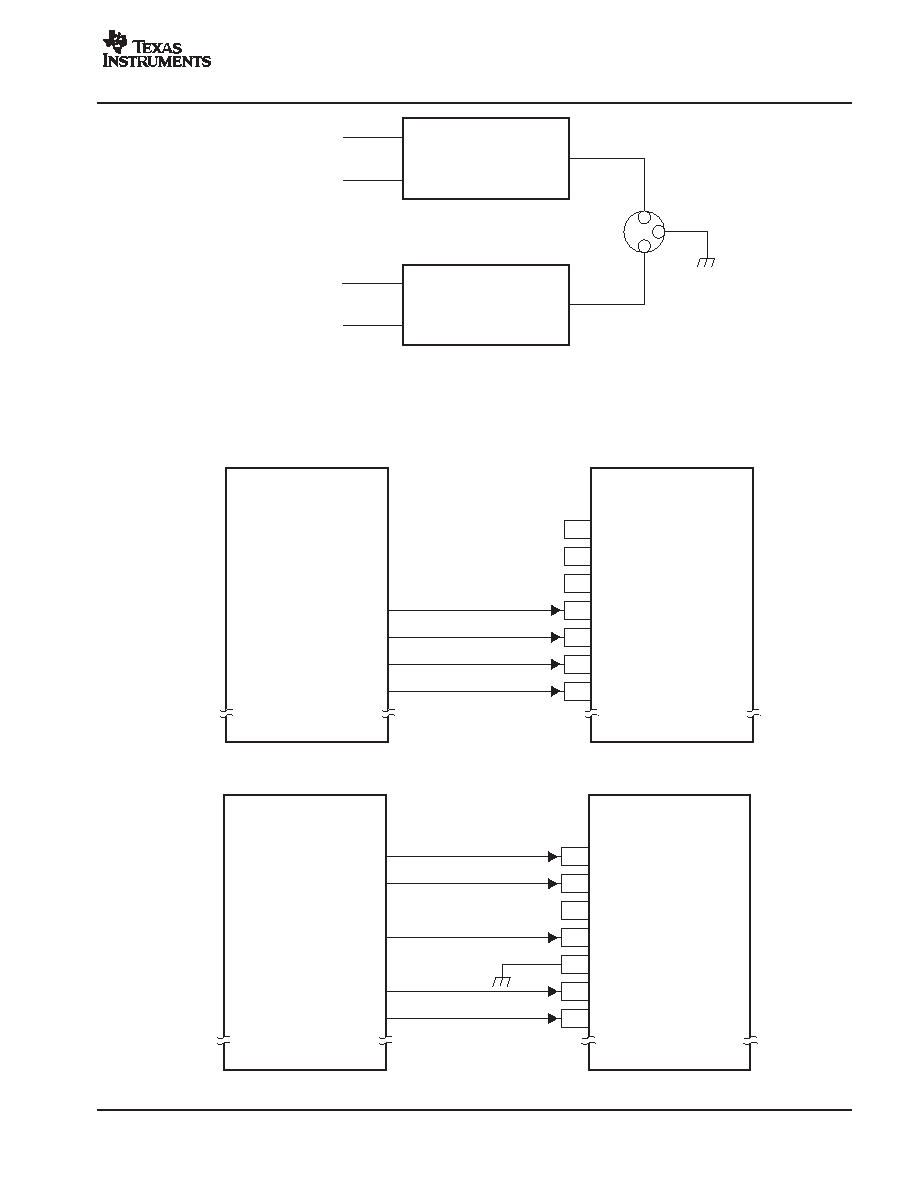

Figure 36. Measurement Circuit for Monaural Mode

APPLICATION FOR EXTERNAL DIGITAL FILTER INTERFACE

DATA

BCK

SCK

WDCK (Word Clock)

External Filter Device

PDATA

5

6

7

PBCK

SCK

DSDL

1

2

3

4

DSDR

DBCK

PLRCK

DSD1792

DFMS = 0

BCK

SCK

WDCK (Word Clock)

External Filter Device

PDATA

5

6

7

PBCK

SCK

DSDL

1

2

3

4

DSDR

DBCK

PLRCK

DSD1792

DFMS = 1

DATA_L

DATA_R

Figure 37. Connection Diagram for External DIgital Filter (Internal DF Bypass Mode) Application

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EL5001IRE-T7

IC CLOCK DRIVER 6-CHAN 20-HTSSOP

FT10001L6X

IC RESET TIMER 6-MICROPAK

FT3001MPX

IC RESET TIMER 8-MLP

FT7521L6X

IC RESET TIMER 7.5SEC 6MICROPAK

FT7522L6X

IC RESET TIMER 6-MICROPAK

FT8010UMX

IC RESET TIMER CONF DELAY 10UMLP

FTS125-COO-010.0M

IC GPS BASED TIMING MOD (OCXO)

FTS125-CTV-010.0M

IC GPS BASED TIMING MOD (TCXO)

相关代理商/技术参数

DSD1792DBG4

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1792DBR

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1792DBRG4

功能描述:音频数/模转换器 IC 24B 192kHz Sampl Adv Segment Aud St DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793

制造商:BB 制造商全称:BB 功能描述:24 BIT 192 KHZ SAMPLING ADVANCED SEGMENT AUDIO STEREO DIGITAL TO ANALOG CONVERTER

DSD1793DB

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBG4

功能描述:音频数/模转换器 IC 24B 192kHz Sampl Adv Segment Aud St DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBR

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

DSD1793DBRG4

功能描述:音频数/模转换器 IC 24-Bit 192kHz Smplng Adv Stg Stereo DAC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel